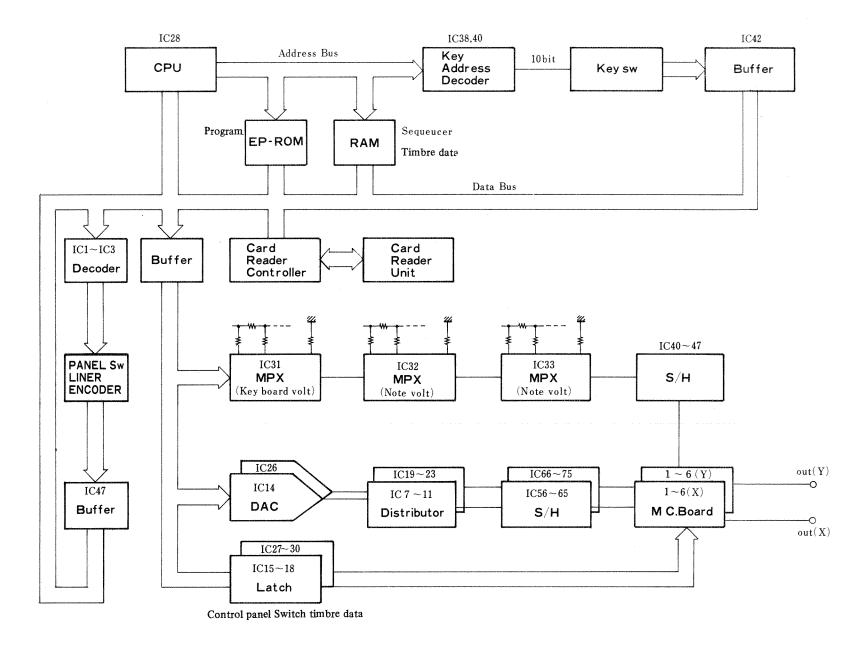

### •OVERALL BLOCK DIAGRAM

Fig. 2

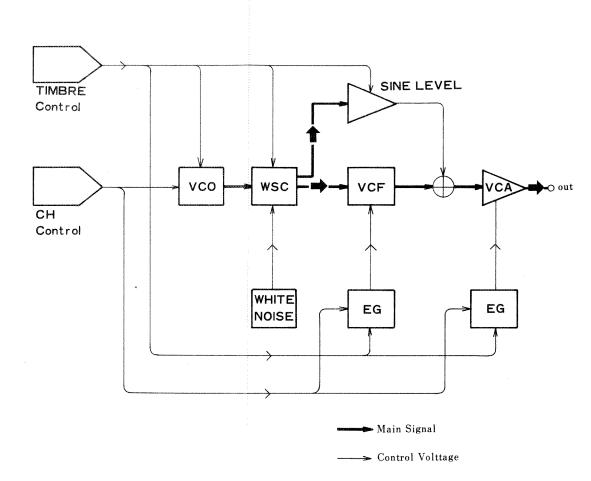

## ● M Circuit Board Block Diagram

Fig. 3

# 2. INDIVIDUAL CIRCUIT DESCRIPTIONS

Refer to the Service Manual circuit diagrams and the overall diagram.

**Keyboard Scanning Circuit** (Service Manual pp.  $32 \sim 34, 70, 71$ )

Unlike conventional synthesizers, the keyboard scanning circuit in the CS70M involves an initial passing of 3-bit address signals from the CPU to the IC38/IC40 keyboard address decoder for addressing. The decoder used here is an IC chip where low level outputs are obtained only when the enable input G1 = H and G2A = G2B (see Table 3). Furthermore, this output is switched to low voltage in succession, generating 10 scanning bits by using another IC chip.

This 10-bit output voltage is then inverted by the data bus buffer, and applied to the respective half-octave terminals of the manual keyboard. If any of the keys is then turned on under these conditions, the key switch is short circuited, and the scanning result subsequently appears at the N1  $\sim$  N7 terminals via a diode circuit.

Decoder Table (for IC single-chip)

| Enable |           | Address<br>Input | Output |     |     |     |     |     |     |     |

|--------|-----------|------------------|--------|-----|-----|-----|-----|-----|-----|-----|

| $G_1$  | $G_{2 A}$ | СВА              | Υ 0    | Y 1 | Y 2 | Y 3 | Y 4 | Y 5 | Y 6 | Y 7 |

| Н      | L         | LLL              | L      | Н   | Н   | Н   | Н   | Н   | Н   | Н   |

| Н      | L         | LLH              | Н      | L   | Н   | Н   | Н   | Н   | Н   | Н   |

| Н      | L         | LHL              | Н      | Н   | L   | Н   | Н   | Н   | Н   | Н   |

| Н      | L         | LHH              | Н      | Н   | Н   | L   | Н   | Н   | Н   | Н   |

| Н      | L         | HLL              | Н      | Н   | Н   | Н   | L   | Н   | Н   | Н   |

| Н      | L         | HLH              | Н      | Н   | Н   | Н   | Н   | L   | Н   | Н   |

| Н      | L         | HHL              | Н      | Н   | Н   | Н   | Н   | Н   | L   | Н   |

| Н      | L         | ННН              | Н      | Н   | Н   | Н   | Н   | Н   | Н   | L   |

Table 3

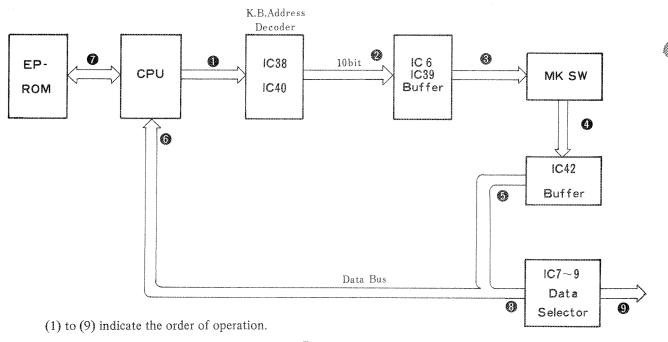

Octaves and notes are thus scanned by the KBD0  $\sim$  KBD9 and N1  $\sim$  N7 terminal matrix, and the results passed to the CPU via the CPU data bus. The CPU addresses key code data in the EP-ROM on the basis of the data bus results, the key code finally being passed to the data selector via the data bus. These steps are summarized in the block diagram in Fig. 4.

## ★ Key board Scan. Block Diagram

Fig. 4